| Case Temperature | Radiation Immunity                                                                                                                         |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| -55°C to +125°C  | TID >100k rad(Si) SEL Immune ≤ 100 MeV-cm <sup>2</sup> /mg SEU Immune ≤ 40 MeV-cm <sup>2</sup> /mg SET Immune ≤ 80 MeV-cm <sup>2</sup> /mg |

#### 1 Features

- 8V-36V eFUSE Power Switch Controller

- Single- or Dual-Supply Operation

- MIL-STD-461 CS106 Compatible to 56V

- Source Power Switching with Inrush current limiting

- Forward Overcurrent and Short Circuit Protection

- <500ns typical short circuit break response</li>

- Optional OR\_FET with Reverse Current Protection

- Line and Load Side Voltage Monitor and Protection

- Optional Digital Voltage and Current Telemetry

- o 10-bit VIN/VOUT/IDS Telemetry (via PMBus®)

- Latching/Retriggerable/Pulsing Power FET Control

- Package Options:

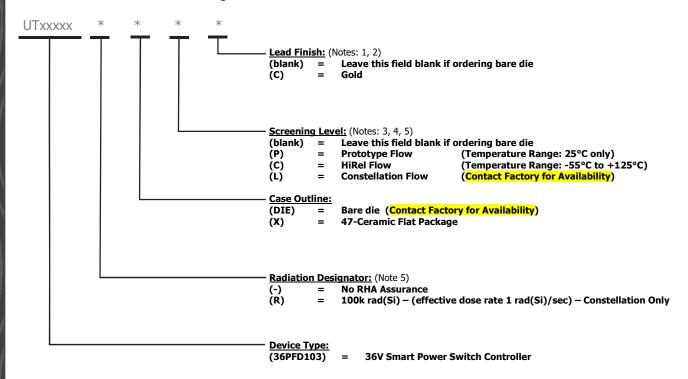

- 47-Lead Dual Flatpack

- o 16.1 x 10.75 mm, 0.635 mm pitch

- $\circ$  Mass = 2.3gm

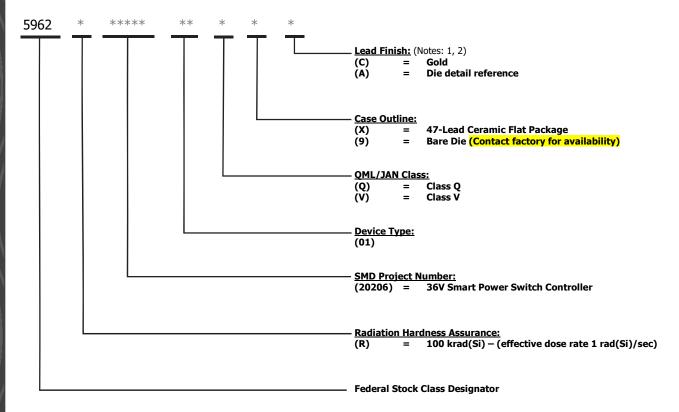

- Standard Microcircuit Drawing: 5962-20206

### 2 Introduction

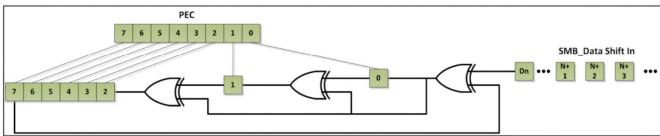

The UT36PFD103 Smart Power Switch Controller (SPSC) is an intelligent PowerMOSFET controller with load-side inrush current limiting and eFuse protection of current faults. An optional Ideal Diode (OR FET) facilitates redundant power architectures such as uninterruptable power supplies. The SPSC accommodates protection of the PowerFET SOA while providing flexible power switching control for a wide range of space applications.

### 3 Applications

- Power Distribution with Short Circuit Protection

- SpaceVPX SpaceUM VS1 (+12V) Power Switching

- Uninterruptable Power Supplies

- Launch-Vehicle Long Power Harness Splicing

- Pyro ARM-FIRE Controller

- Thruster and Waveguide Actuation Controller

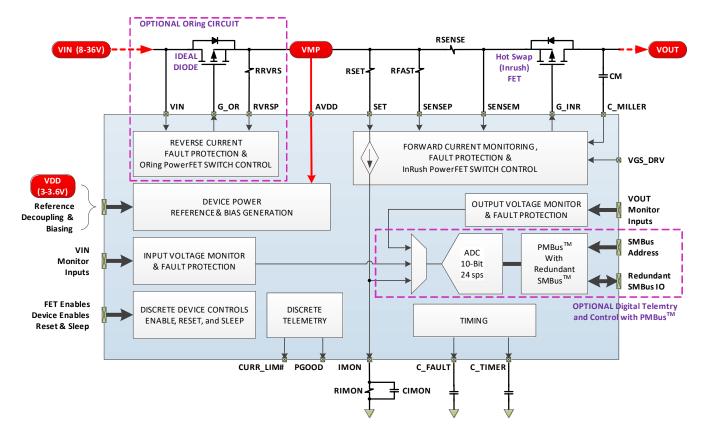

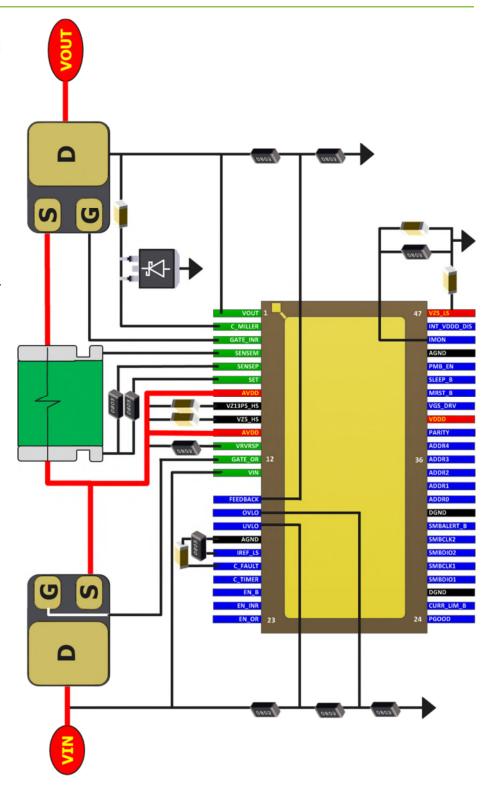

Figure 1-3-1. UT36PFD103 Block Diagram

# UT36PFD103

### **TABLE OF CONTENTS**

| 1  | Fe              | atures                                                                                        | 1  |

|----|-----------------|-----------------------------------------------------------------------------------------------|----|

| 2  | Int             | troduction                                                                                    | 1  |

| 3  | Ap              | pplications                                                                                   | 1  |

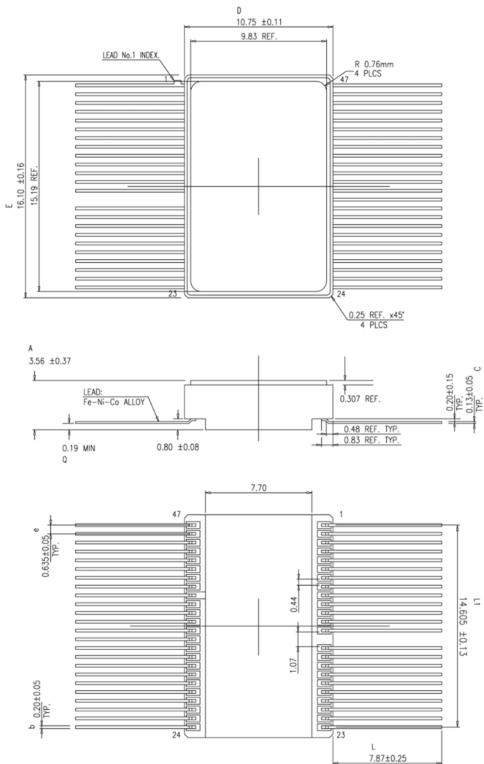

| 4  | Pir             | nout Package Arrangement                                                                      | 5  |

| 5  | Pir             | nlist                                                                                         | 5  |

| 6  | Fu              | ınctional Overview                                                                            | 11 |

|    | 6.1             | Load Slew Rate Control and Inrush Current Limiting                                            | 11 |

|    | 6.2             | OR FET Switch                                                                                 | 11 |

|    | 6.3             | Forward Current Monitoring                                                                    | 12 |

|    | 6.4             | Overcurrent Fault Protection                                                                  | 12 |

|    | 6.5             | Short Circuit Break Fault Protection                                                          | 12 |

|    | 6.6             | Voltage Fault Protection                                                                      | 13 |

|    | 6.7             | Voltage Monitoring                                                                            | 13 |

|    | 6.8             | PMBus                                                                                         | 13 |

| 7  | Ab              | osolute Maximum Ratings (1, 2)                                                                | 14 |

| 8  | Op              | perational Environment                                                                        | 14 |

| 9  | Re              | ecommended Operating Conditions (1)                                                           | 15 |

| 10 | )               | Electrical Characteristics (1)                                                                | 15 |

| 11 |                 | Timing Characteristics                                                                        | 25 |

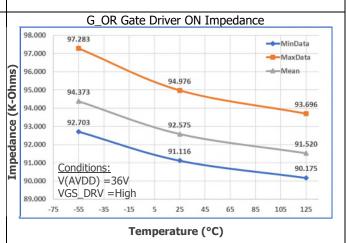

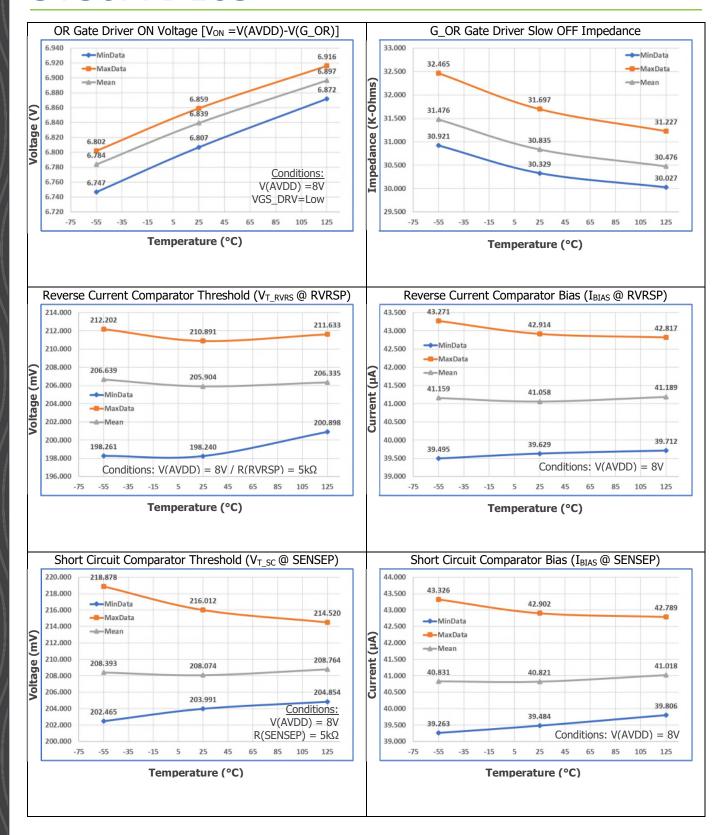

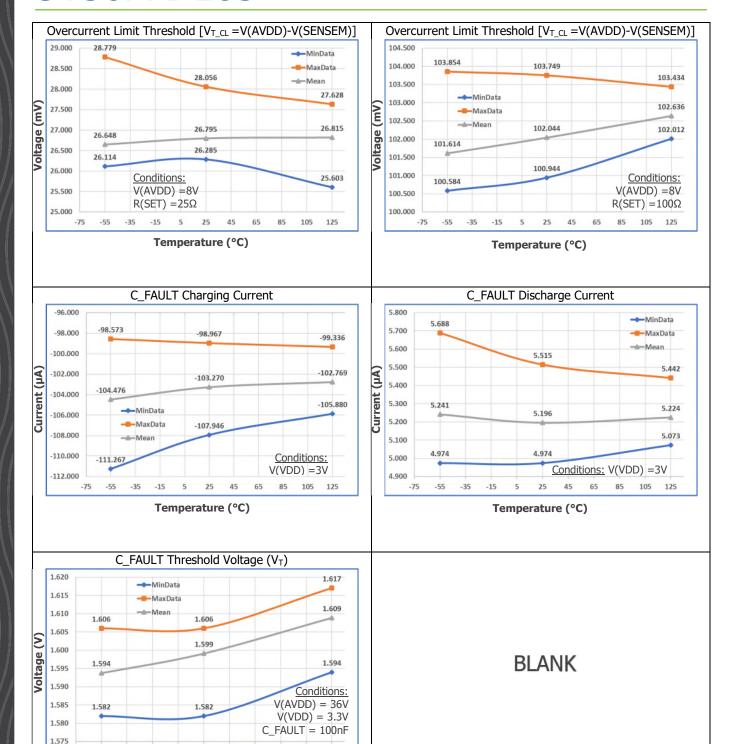

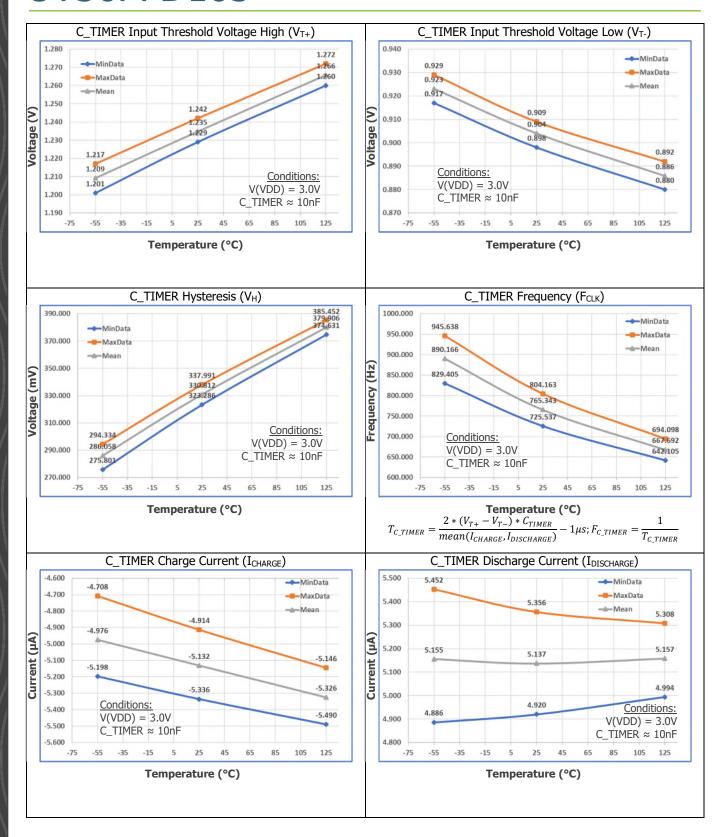

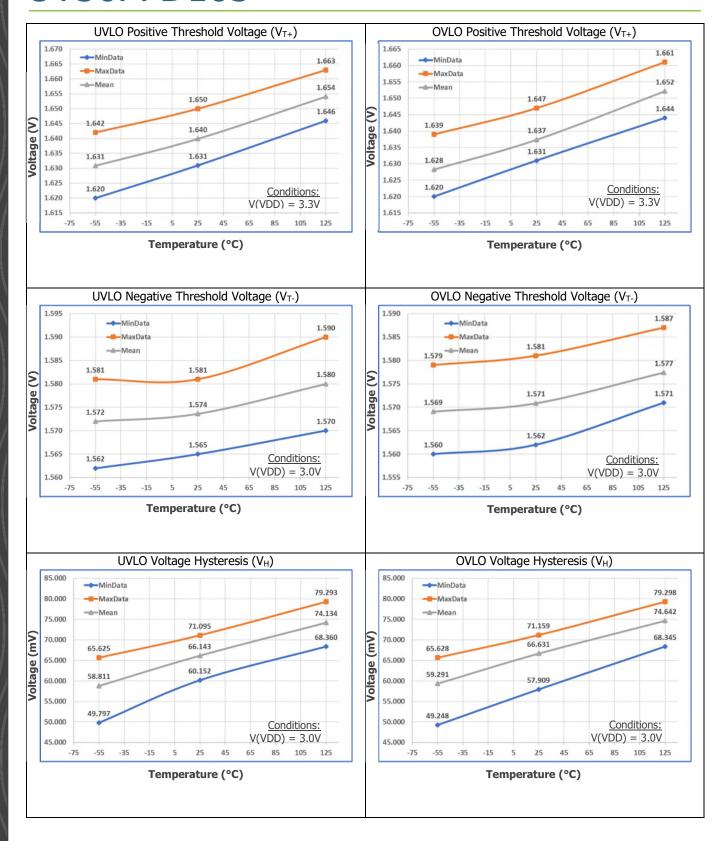

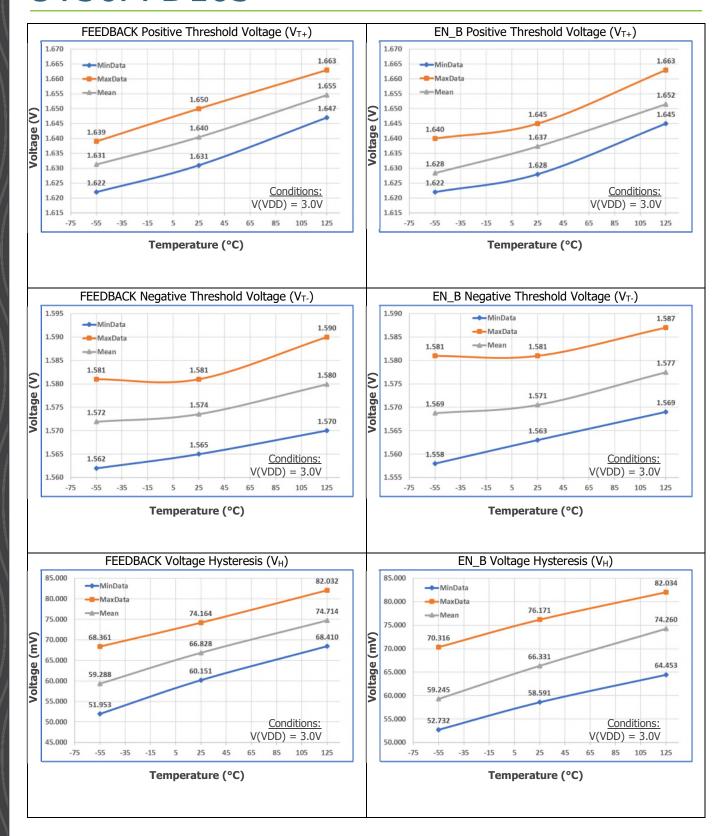

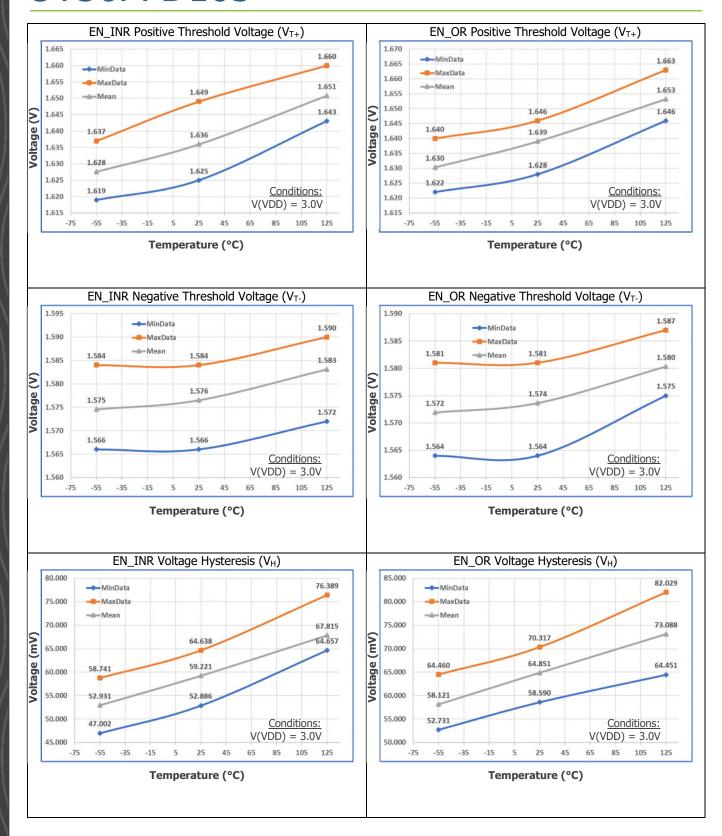

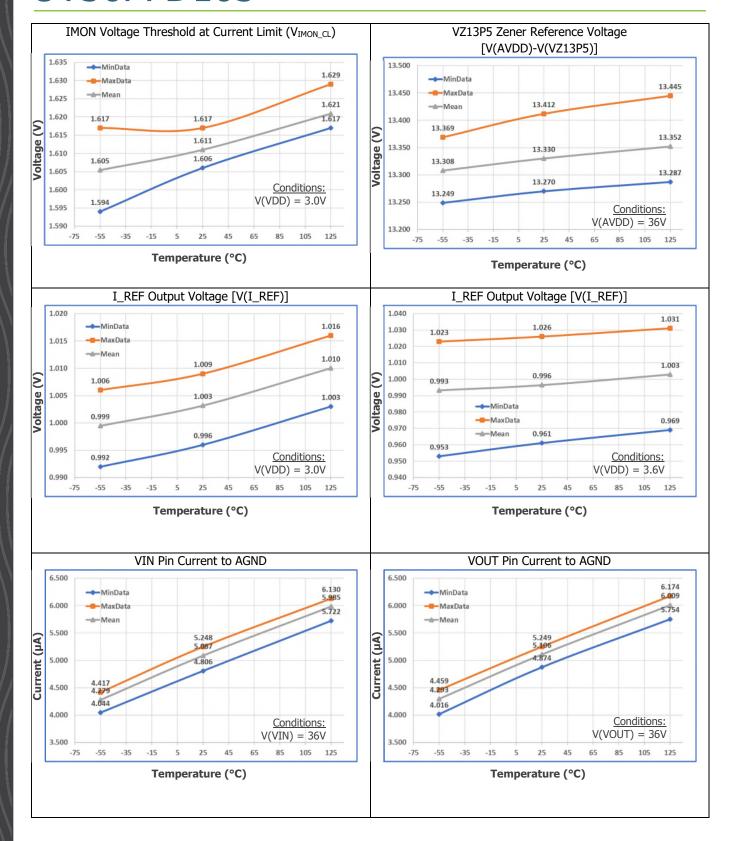

| 12 | 2               | Typical Performance Characteristics (1) Sample Size for most of the following charts is N>=95 | 34 |

| 13 | }               | Detailed Functional Description                                                               | 47 |

|    | 13.1            | PMBus® / SMBus Functional Description                                                         | 47 |

|    | 13              | 3.1.1 PMBus Command Definitions                                                               | 51 |

|    | 13              | 3.1.2 SMBus Ternary Addressing with Parity                                                    | 60 |

|    | <mark>13</mark> | S.1.3 SMBus Address Resolution Protocol (ARP) and Unique Device Identification (UDID)         | 62 |

| 14 | }               | Application Configurations                                                                    | 66 |

| 15 | ;               | Packaging Drawings                                                                            | 68 |

| 16 | •               | Ordering information                                                                          | 69 |

|    | 16.1            | CAES Part Number                                                                              | 69 |

|    | 16.2            | SMD Part Number                                                                               | 70 |

| 17 | ,               | Revision History                                                                              | 71 |

| Da | ate             |                                                                                               | 71 |

| Ve | ersion          | ٦                                                                                             | 71 |

| Ed | litor .         |                                                                                               | 71 |

| Da | atash           | eet Level                                                                                     | 71 |

| Ch | nange           | e Description                                                                                 | 71 |

# **UT36PFD103**

### **TABLE OF FIGURES**

| igure 1-3-1. UT36PFD103 Block Diagram                                                        | 2  |

|----------------------------------------------------------------------------------------------|----|

| igure 4-1. Package Pinout with Signal Groupings                                              | 5  |

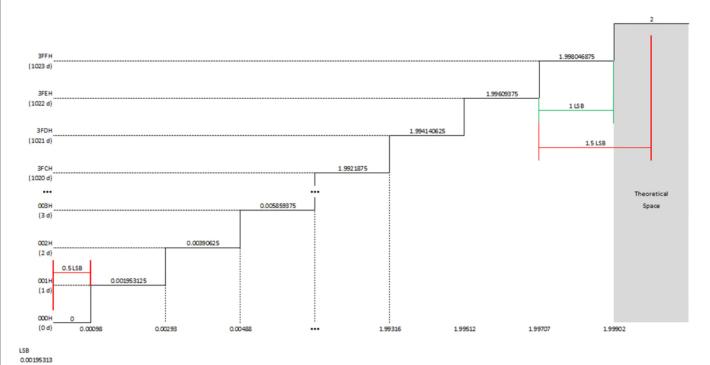

| Figure 10-1. ADC Ideal Transfer Function                                                     | 24 |

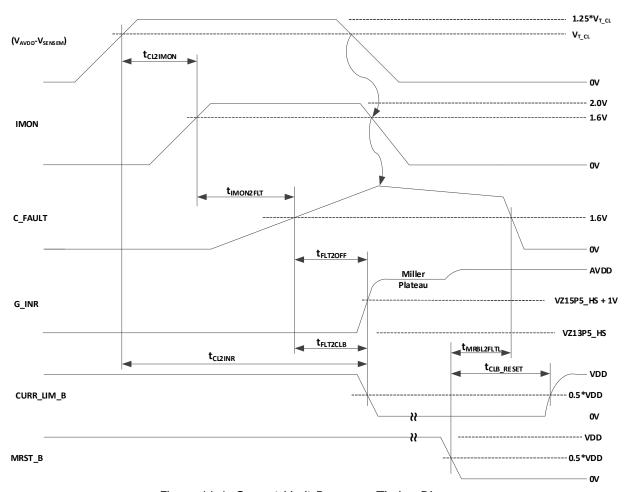

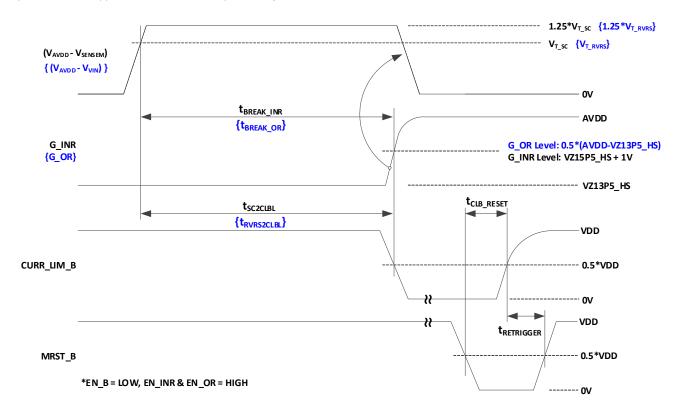

| igure 11-1. Current Limit Response Timing Diagram                                            | 25 |

| igure 11-2. Reverse Current and Short Circuit Break Timing Diagram                           | 26 |

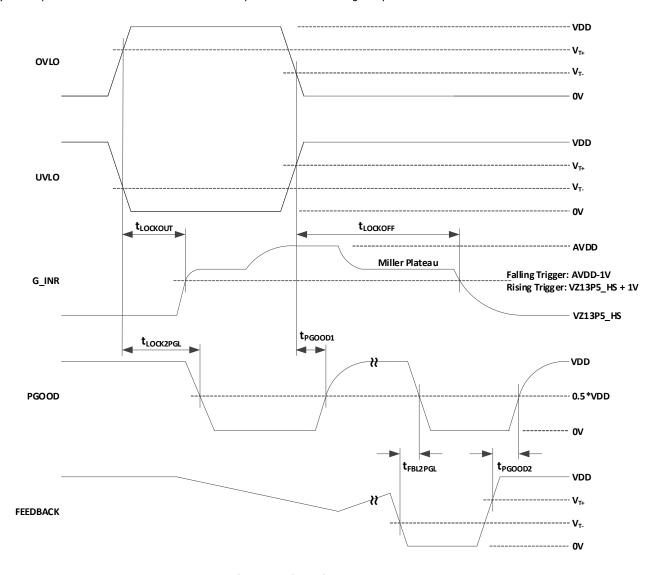

| igure 11-3. Voltage Fault and PGOOD Timing Diagram                                           | 27 |

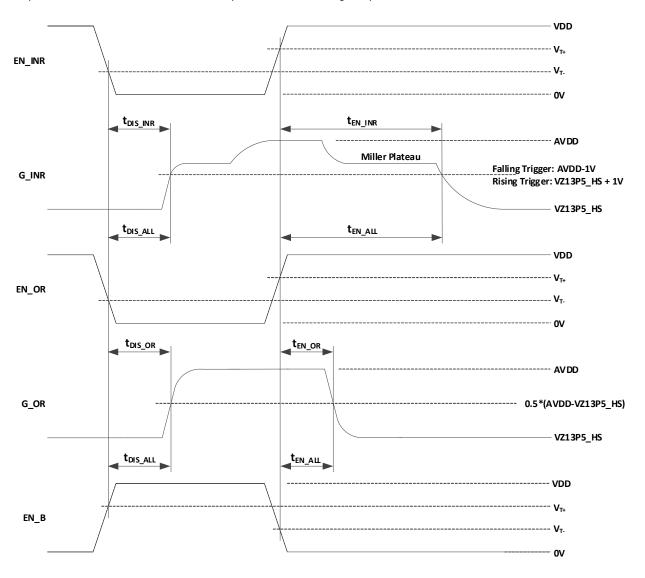

| igure 11-4. Commanded Enable and Disable Timing Diagram                                      | 28 |

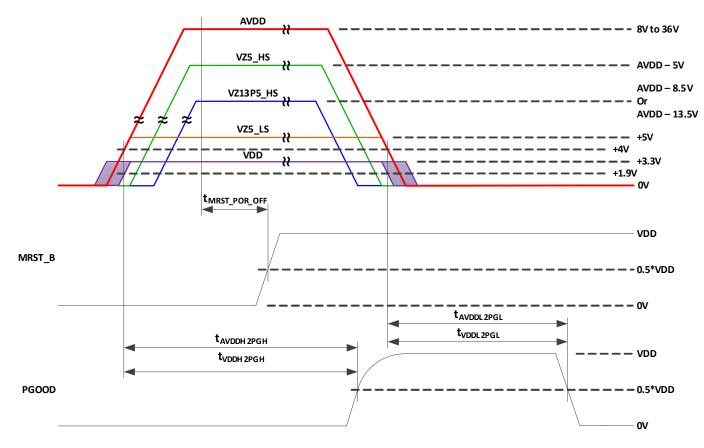

| igure 11-5. Power Up/Down and Reset Timing Diagram                                           | 29 |

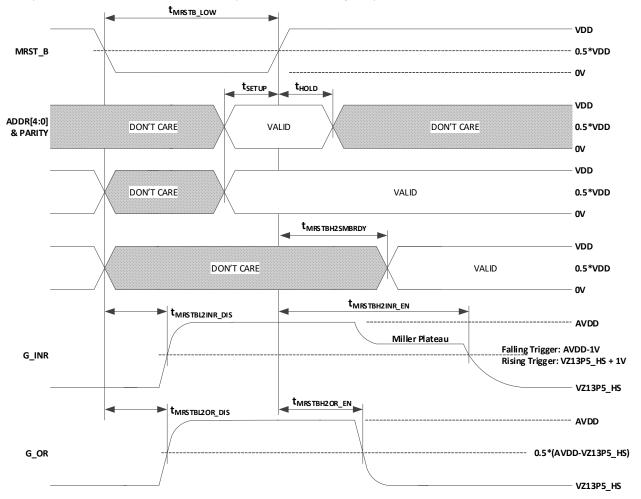

| igure 11-6. Master Reset Timing Diagram                                                      | 30 |

| igure 11-7. Sleep Timing Diagram                                                             | 31 |

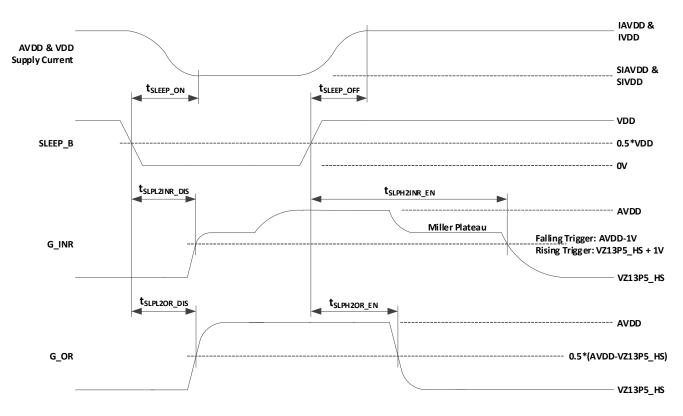

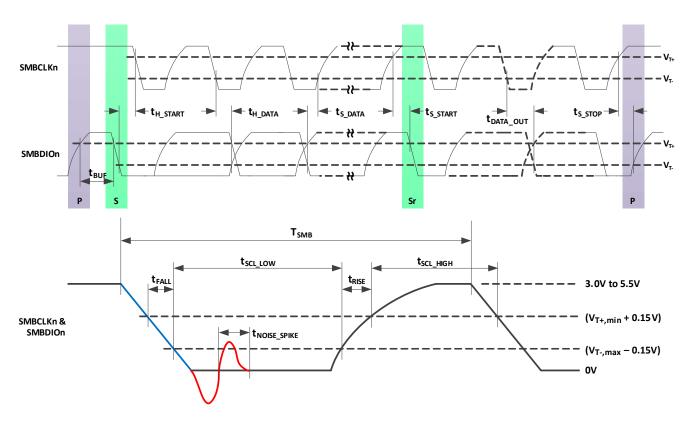

| igure 11-8. SMBus Timing Diagram                                                             |    |

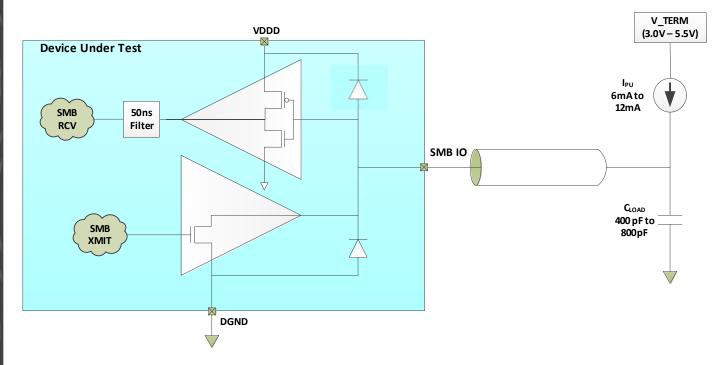

| igure 11-9. SMBus IO Test Load                                                               |    |

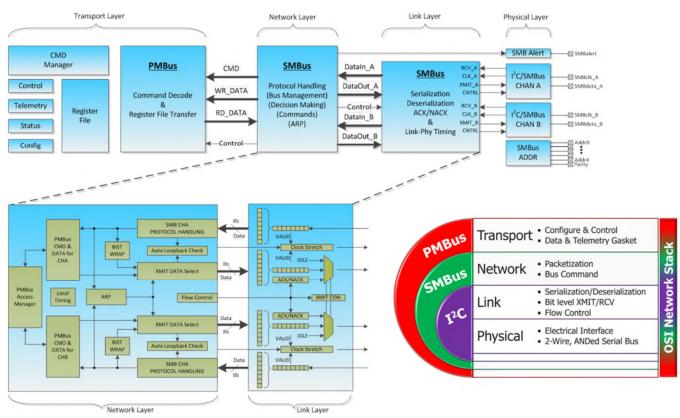

| igure 13-1. SPSC PMBus™ / SMBus Block Diagram                                                | 47 |

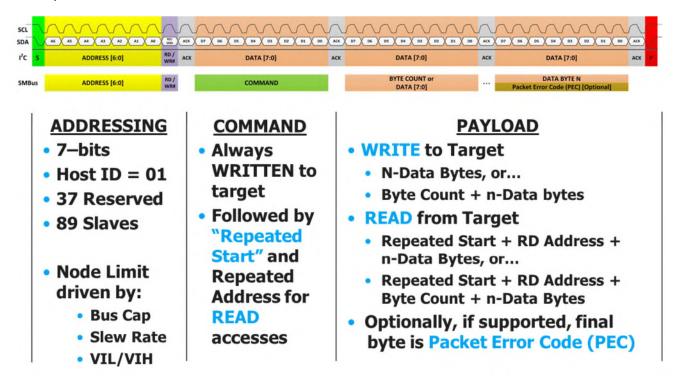

| igure 13-2. PMBus™ / SMBus System At a Glance                                                | 48 |

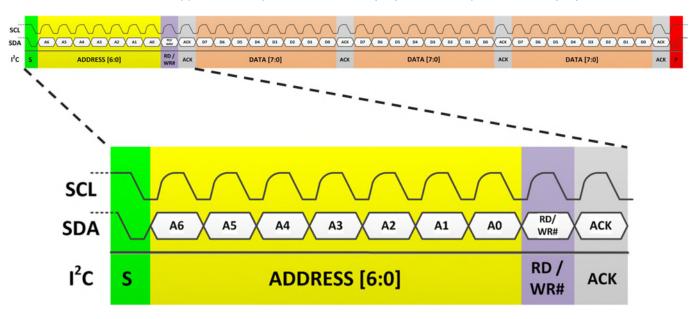

| igure 13-3. I <sup>2</sup> C Address Byte Formatting                                         | 48 |

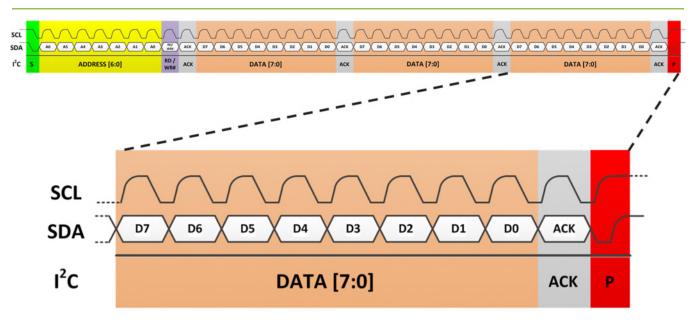

| Figure 13-4. I <sup>2</sup> C Data Byte Formatting                                           |    |

| Figure 13-5. SMBus Network Layer Protocol Formatting Summary                                 | 49 |

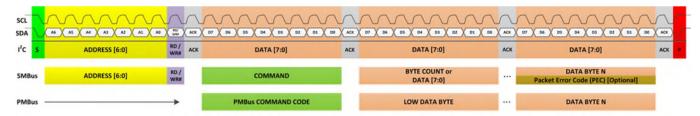

| Figure 13-6. PMBus Protocol Formatting and Supported Commands                                | 50 |

| Figure 13-7. ARP <b>GENERAL</b> GET UDID Command with SPSC Ternary Address 29h (41 decimal)  | 64 |

| Figure 13-8. ARP <b>DIRECTED</b> GET UDID Command with SPSC Ternary Address 29h (41 decimal) | 65 |

| Figure 14-1. Essential Hot Swap Controller Configuration with eFuse Fault Protection         | 66 |

| Figure 14-2. Essential SPSC Load-Switch control with                                         | 67 |

| igure 15-1: 47-Lead Flatpack Outline Drawing                                                 | 68 |

### 4 Pinout Package Arrangement

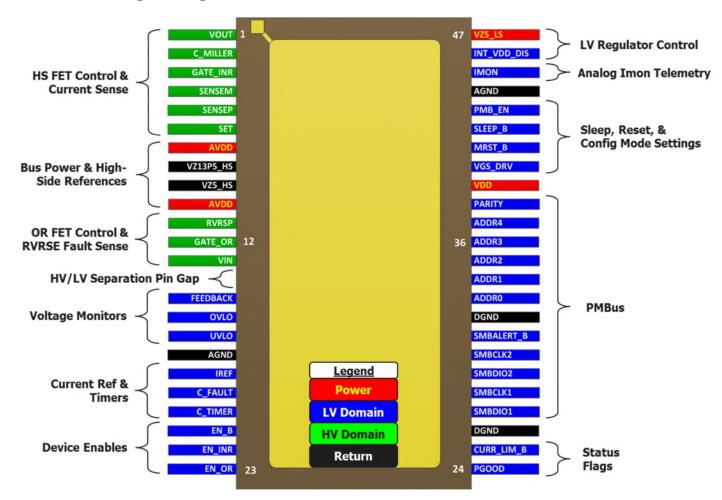

Figure 4-1. Package Pinout with Signal Groupings

### 5 Pinlist

Table 5-1: Pin Type Legend

| Abbreviation | Description                      |

|--------------|----------------------------------|

| IPU          | CMOS Input with Internal Pull-Up |

| I            | CMOS Compatible Input            |

| OD           | Open Drain Output                |

| SMIO         | SMBus IO                         |

| SMI          | SMBus Input                      |

| SMO          | SMBus Output                     |

| TERN         | Ternary Inputs                   |

| AI           | Analog Input                     |

| AI           | Analog Input                     |

| AO           | Analog Output                    |

| AIO          | Analog Input/Output              |

| P            | Power                            |

# **UT36PFD103**

Table 5-2: Pin Definitions (Note 1)

| Number | Number Name Type Active Description |                                               |          |                                                                                                                                                                                                                                                                                   |  |  |  |

|--------|-------------------------------------|-----------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 26, 32 | DGND                                | Р                                             | - Active | Digital ground return pins.                                                                                                                                                                                                                                                       |  |  |  |

| 17, 44 | AGND                                | P                                             |          | Analog ground return pins. These pins need to be connected to a quiet ground plane on the PCB.                                                                                                                                                                                    |  |  |  |

| 7, 10  | AVDD                                | P<br>(Reference to<br>AGND)                   | -        | 8V-36V High voltage input power supply to chip provided from VIN power line in single FET power switching application or SOURCE terminal of ORing FET in ORing applications.                                                                                                      |  |  |  |

| 39     | VDD/CBYP                            | P (Reference to DGND)                         | -        | Bypass capacitor and VDD pin. A bypass capacitor must be connected from this pin to GND if internal 3.3V regulator is enabled. This pin must be connected to external 3.3V power supply if internal regulator is disabled i.e. INT_VDD_DIS is forced to VZ5_LS, high (5V typical) |  |  |  |

| 46     | INT_VDD_DIS                         | I (Power domain VZ5_LS reference to DGND)     | -        | Internal 3.3V regulator disable pin. Connecting this pin to VZ5_LS pin will disable the internal 3.3V regulator. If this pin is tied to GND the internal 3.3V regulator is enabled. A bypass capacitor will be required from VDD/CBYP pin to DGND.                                |  |  |  |

| 9      | VZ5_HS                              | P<br>(Reference to<br>AVDD domain)            |          | Internal high side Zener based regulated supply typically 5V below AVDD. Bypass cap required from this pin to AVDD.                                                                                                                                                               |  |  |  |

| 8      | VZ13P5_HS                           | P (Reference to AVDD domain)                  |          | Internal high side Zener based regulated supply typically 13.5V below AVDD. Bypass cap required from this pin to AVDD                                                                                                                                                             |  |  |  |

| 47     | VZ5_LS                              | P<br>(Reference to<br>AGND)                   |          | Internal low side Zener based regulated supply typically 5V with reference to AGND. It is driven from AVDD. Bypass cap required from this pin to AGND.                                                                                                                            |  |  |  |

| 18     | IREF                                | AI  (Power domain  VDD reference to  AGND)    | -        | A nominally 1V reference pin that sets the device's precision bias current when a 24.9K $\Omega$ resistor is connected from this pin to AGND. This pin also represer 50% of the ADC voltage reference.                                                                            |  |  |  |

| 5      | SENSEP                              | AI  (Power domain  AVDD reference to  VZ5_HS) | -        | Fast trip sense pin for very high current limit. External resistor is connected from positive terminal of sense resistor to this pin.                                                                                                                                             |  |  |  |

| 6      | SET                                 | AI  (Power domain  AVDD reference to  VZ5_HS) | -        | Current limit programming pin. External resistor is connected from positive terminal of sense resistor to this pin.                                                                                                                                                               |  |  |  |

| 4      | SENSEM                              | AI  (Power domain  AVDD reference to  VZ5_HS) | -        | Negative terminal of sense resistor and source of load PCH_MOSFET                                                                                                                                                                                                                 |  |  |  |

| 3      | GATE_INR                            | AO (Power domain AVDD reference to VZ13P5_HS) | -        | Gate driver output for external inrush switch PCH_MOSFET                                                                                                                                                                                                                          |  |  |  |

| Number | Name       | Туре                                             | Active | Description                                                                                                                                                                                                                                                                                                 |

|--------|------------|--------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2      | C_MILLER   | AO                                               | -      | Slew-rate limiting miller capacitor                                                                                                                                                                                                                                                                         |

|        |            | (Power domain<br>AVDD reference to<br>VZ13P5_HS) |        |                                                                                                                                                                                                                                                                                                             |

| 11     | RVRSP      | AI  (Power domain  AVDD reference to  VZ5_HS)    | -      | Positive reverse current detection pin. External resistor is connected from positive terminal of sense resistor / source of ORing PCH power FET to this pin.                                                                                                                                                |

| 12     | GATE_OR    | AO  (Power domain  AVDD reference to  VZ13P5_HS) | -      | Gate driver output for external ORING switch PCH_MOSFET                                                                                                                                                                                                                                                     |

| 45     | IMON       | AIO  (Power domain  VDD reference to  AGND)      | -      | Analog current monitor and current limit adjustable pin. A $1.6 \mathrm{K}\Omega$ resistor is connected from this pin to AGND. Ratio of this resistor to SET pin resistor programs the threshold for current limit                                                                                          |

| 24     | PGOOD      | OD  (Power domain  VDD reference to  DGND)       | HIGH   | Power GOOD status (active high open drain). True when internal device power domains and VIN, and FEEDBACK (e.g. VOUT) are within their operating range as set by voltage dividers. This pin can be used to drive enable pin for other devices.                                                              |

| 25     | CURR_LIM_B | OD  (Power domain VDD reference to DGND)         | LOW    | Active low open drain output. When LOW, this pin indicates a current limit fault.                                                                                                                                                                                                                           |

| 19     | C_FAULT    | AIO  (Power domain  VDD reference to  AGND)      |        | Adjustable fault timer for over-current timeout. A capacitor connected from this pin to AGND will set the pulse width for the analog current limit timer. This timer gets activated if the over-current limit is detected. When nothing is connected to this pin, then the default timer is set internally. |

| 20     | C_TIMER    | AIO  (Power domain  VDD reference to  DGND)      |        | Capacitor connected from this pin to DGND will program the clock frequency of a local oscillator to be used in timer circuits.                                                                                                                                                                              |

| 40     | VGS_DRV    | I<br>(Power domain<br>VDD reference to<br>DGND)  | -      | CMOS inputs VGS_DRV will set the VGS drive on external PCH_FET switch. When high, sets VZ13P5_HS to 13.5V below AVDD, typical. When low, sets VZ13P5_HS to 8.7V below AVDD, typical.                                                                                                                        |

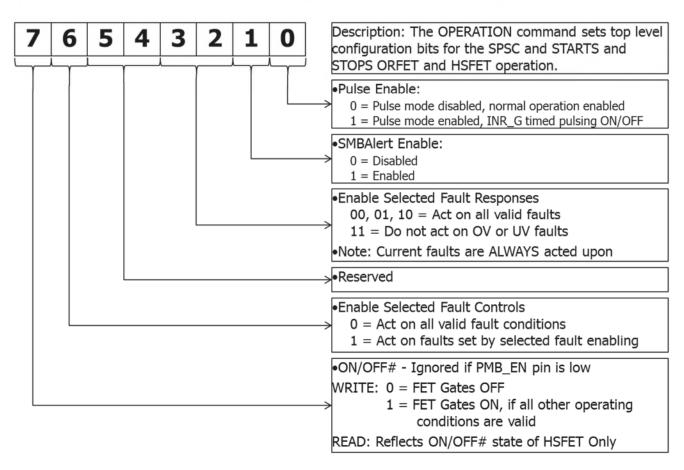

| 22     | EN_INR     | AI  (Power domain  VDD reference to  AGND)       | -      | Active high input to enable inrush gate driver. This enable input is logically combined with EN_B and PMBUS serial interface operation command register ON/OFF bit 7.                                                                                                                                       |

| 23     | EN_OR      | AI  (Power domain  VDD reference to  AGND)       | -      | Active high input to enable ORing gate driver. This enable input is logically combined with the EN_B and PMBUS serial interface operation command register ON/OFF bit 7.                                                                                                                                    |

| Number | Name     | Туре                                             | Active | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|----------|--------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21     | EN_B     | AI<br>(Power domain<br>VDD reference to<br>AGND) | LOW    | Active low master device enable input. The active state of this pin, combined with the active state of EN_INR, EN_OR, and PMBus Operation Register Bit 7 determines if the FET gate controls can be driven active.                                                                                                                                                                                                                                                |

|        |          |                                                  |        | For Pulse Mode applications: If this pin is tied to AGND the on/off pulsing duration may be controlled by the PMBUS serial interface. If EN_B pin is driven by micro controller open drain output and PMB_EN is tied to AGND, the on/off pulsing duration is adjusted by external R and C connected to EN_B pin.                                                                                                                                                  |

| 13     | VIN      | AI<br>(Power domain<br>VDD reference to<br>AGND) | -      | Source input bus voltage to internal ADC. The voltage on this input is scaled by 20:1 V/V and passed as VOUT telemetry to the 10-bit ADC.  Internal measurements of this pin voltage are only accessible through PMBus.                                                                                                                                                                                                                                           |

| 16     | UVLO     | AI  (Power domain  VDD reference to  AGND)       | -      | Under Voltage Lock Out pin monitors the voltage VIN (Power supply) for Under Voltage fault. A resistor voltage divider from VIN to AGND is compared with internal VREF. If voltage on UVLO gets below the UVLO threshold level the load FET gate and output will be disabled.                                                                                                                                                                                     |

| 15     | OVLO     | AI  (Power domain  VDD reference to  AGND)       | -      | Over Voltage Lock Out pin monitors the voltage VIN (Power supply) for Over Voltage fault. A resistor voltage divider from VIN to AGND to be compared with internal VREF. If voltage on OVLO exceeds the OVLO threshold level the load FET gate and output will be disabled.                                                                                                                                                                                       |

| 1      | VOUT     | AI  (Power domain  VDD reference to  AGND)       | -      | Monitor input to the switched load side supply voltage. The voltage on this input is scaled by 20:1 V/V and passed as VOUT telemetry to the 10-bit ADC.  Internal measurements of this pin voltage are only accessible through PMBus.                                                                                                                                                                                                                             |

| 14     | FEEDBACK | AI  (Power domain  VDD reference to  AGND)       |        | Output feedback voltage. Resistor divider from LOAD PFET Drain Terminal to this pin determines if the LOAD voltage is above its minimum allowable operating voltage. If the voltage drops below the set value, PGOOD output will fall LOW. If FEEDBACK is under its threshold voltage, no action will be taken to affect the load FET gate driver.                                                                                                                |

| 41     | MRST_B   | I (Power domain VDD reference to DGND)           | LOW    | Active low master reset pin. When driven low, this pin turns off the external power FETs with a strong driver, clears any faults conditions, and places all internal logic states to their POR condition.                                                                                                                                                                                                                                                         |

| 42     | SLEEP_B  | IPU  (Power domain  VDD reference to  DGND)      | LOW    | Active low digital input. If SLEEP_B pin is driven LOW, SPSC is put in lowest power sleep mode, disabling some of the internal circuits, and both external power FETs will be disabled. Active analog and PMBUS circuits will be in low power mode. If this pin is set to high digital level, or left floating, SPSC device operates normally, actively controlling inrush and ORing power FETs, based on power good status, voltage monitoring and fault status. |

| 43     | PMB_EN   | I<br>(Power domain<br>VDD reference to<br>DGND)  | HIGH   | Active high PMBus Enable pin. If PMB_EN pin is connected to DGND, the PMBus circuitry is disabled and all PMBus oriented functions are blocked from affecting device operation. If PMB_EN pin is connected to VDD; it enables the PMBus and all associated functions to include the SMBus interface.                                                                                                                                                              |

| Number | Name       | Туре                                              | Active | Description                                                                                                            |

|--------|------------|---------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------|

| 27     | SMBDIO1    | SMIO (Power domain VDD reference to DGND)         | -      | SMBus bi-directional data for side 1. Open drain, 5V tolerant.                                                         |

| 28     | SMBCLK1    | SMI<br>(Power domain<br>VDD reference to<br>DGND) | -      | SMBus clock input for side 1. Open drain, 5V tolerant.                                                                 |

| 31     | SMBALERT_B | SMO (Power domain VDD reference to DGND)          | LOW    | Active low SMBus alert output. Open drain, 5V tolerant.                                                                |

| 29     | SMBDIO2    | SMIO  (Power domain  VDD reference to  DGND)      | -      | SMBus bi-directional data for side 2. Open drain, 5V tolerant.                                                         |

| 30     | SMBCLK2    | SMI  (Power domain  VDD reference to  DGND)       | -      | SMBus clock input for side 2. Open drain, 5V tolerant.                                                                 |

| 37     | ADDR4      | TERN  (Power domain  VDD reference to  DGND)      | -      | Ternary address line 4 for device address ID; It has 3 state, connect to digital supply (VDD), DGND, or left floating. |

| 36     | ADDR3      | TERN  (Power domain  VDD reference to  DGND)      | -      | Ternary address line 3 for device address ID; It has 3 state, connect to digital supply (VDD), DGND, or left floating. |

| 35     | ADDR2      | TERN  (Power domain  VDD reference to  DGND)      | -      | Ternary address line 2 for device address ID; It has 3 state, connect to digital supply (VDD), DGND, or left floating. |

| 34     | ADDR1      | TERN  (Power domain  VDD reference to  DGND)      | -      | Ternary address line 1 for device address ID; It has 3 state, connect to digital supply (VDD), DGND, or left floating. |

| 33     | ADDR0      | TERN (Power domain VDD reference to DGND)         | -      | Ternary address line 0 for device address ID; It has 3 state, connect to digital supply (VDD), DGND, or left floating. |

# UT36PFD103

| Number | Name   | Туре                                            | Active | Description                                                                                                                                                                                                                                 |

|--------|--------|-------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38     | PARITY | I<br>(Power domain<br>VDD reference to<br>DGND) | -      | Odd parity bit for equivalent terminal address defined by the 5-bit ternary decoder. This parity bit will be evaluated against the ternary set address when the SPSC exits reset.                                                           |

|        |        |                                                 |        | If parity is good and the address is not reserved, the SPSC SMBus will take the pin-programmed address. If parity is bad and/or the address is reserved, the SPSC SMBus address will take on the SMBus special "DEFAULT ADDRESS: 1100001b". |

Note:

1) The SPSC is offered in a 47-Lead Flatpack providing an unpopulated pin gap between pins 13 and 14 to reduce the risk of shorting signals on the high-voltage domain to those on the low-voltage domain. The gap also helps ensure proper device orientation and reference for debug.

### 6 Functional Overview

The Smart Power Switch Controller (SPSC) provides a single device solution for controlling the gate of P-Channel Power MOSFETs while ensuring they remain within their specified Safe Operating Areas (SOAs). Combining adjustable current and voltage monitoring capability with flexible fault detection, isolation, and recovery, the SPSC integrates many of the critical functions required for power switching applications and often implemented with a number of discrete components. By integrating essential voltage and current monitoring the SPSC is able to reliably enable/disable the Power Switching MOSFET in accordance with detected fault conditions while providing telemetry to the power system manager. The following sections provide a brief summary of the major functional blocks making up the Smart Power Switch Controller.

### 6.1 Load Slew Rate Control and Inrush Current Limiting

The fundamental responsibility of the power switch controller is to turn a power bus isolating switch ON and OFF when commanded. To this end, the SPSC drives the gate of a P-Channel Power MOSFET (PFET) to establish/break the connection between the power line and a load. The SPSC monitors a variety of sources to determine if the LOAD switch should be ON or OFF.

When commanded to turn the switch ON, a Miller capacitor connected between the C\_MILLER pin and PFET DRAIN (LOAD side) terminal will limit the inrush current which results when the input supply charges the load capacitance. By knowing the application overcurrent limit ( $I_{LIM}$ ) or target peak inrush current, the C<sub>MILLER</sub> value is calculated as follows:

Where  $V_T$  is the threshold voltage of the external PowerFET;  $V_{GATE}$ ,  $R_{PD}$ ,  $R_{PU}$ , and  $I_{BOOT}$  are gate driver characteristics specified in the electrical tables later in this datasheet.  $C_{LOAD}$  and  $I_{LIM}$  are application dependent.

Alternatively, if you know the rate at which you want to ramp the load voltage, you can calculate CMILLER with the following equation:

Normally, the user would select a miller capacitor value that satisfies the desired ramp rate and current limit. Additionally, it is strongly recommended for the user to include a series 1.5k-ohm resistor between the C\_MILLER pin and the CMILLER capacitor. This resistor behaves as a current limiter for transient currents that may pass through the miller capacitor into the C\_MILLER pin during a rapid, short circuit, eFusing event of the load.

#### 6.2 OR FET Switch

In many applications, especially those that are spaceborne, redundancy and cross strapping systems are extremely important. The SPSC includes the ability to control a second, ORing, PFET to provide an ideal diode function. When enabled and as long as monitored voltage and currents are appropriate, the SPSC will activate the ORing FET. If a reverse current is detected the OR FET will be disabled.

The proper orientation of the ORing PFET is to have common source configuration with the Hot Swap PFET connecting the LOAD side supply (as shown in Figure 1-3-1). This ensures the highest input line power will reach the Source terminal on the LOAD switch, powering the SPSC while blocking unintentional power to the load and reverse powering a redundant, disabled, or lower voltage line supply.

If the application doesn't require ORing, the feature can be disabled by driving the EN\_OR pin low and connecting RVRSP and AVDD to VIN.

## **UT36PFD103**

### 6.3 Forward Current Monitoring

By installing a current sensing resistor in series with the input power line and the LOAD PFET Source terminal and by connecting a gain setting resistor from the SET pin to the input power line, the user can measure the line-to-load current through the SPSC. Using the voltage drop across the sense resistor, the SPSC mirrors a proportional current to the IMON pin. With a  $1.6 \text{K}\Omega$  resistor connected between the IMON pin and GND, a voltage proportional to the load current is produced.

To set the desired line-load current limit, the user selects a SET resistor that produces a 1mA current when the voltage drop across the sense resistor is reached at the current limit. In equation form, the SET resistor is determined by:

$$Rset = \frac{Rsense*Ilimit}{1mA}$$

The line-load current limit state occurs when  $V_{IMON}$  exceeds 1.6V. This occurs when 1mA flows through the 1.6Kohm resistor from IMON pin to AGND.

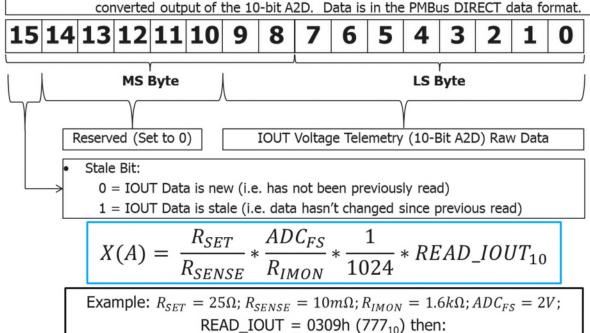

The user can either measure the IMON voltage to determine the current through the LOAD FET using the equation:

$$I_{LOAD} = \frac{V_{IMON} * R_{SET}}{R_{IMON} * R_{SENSE}}$$

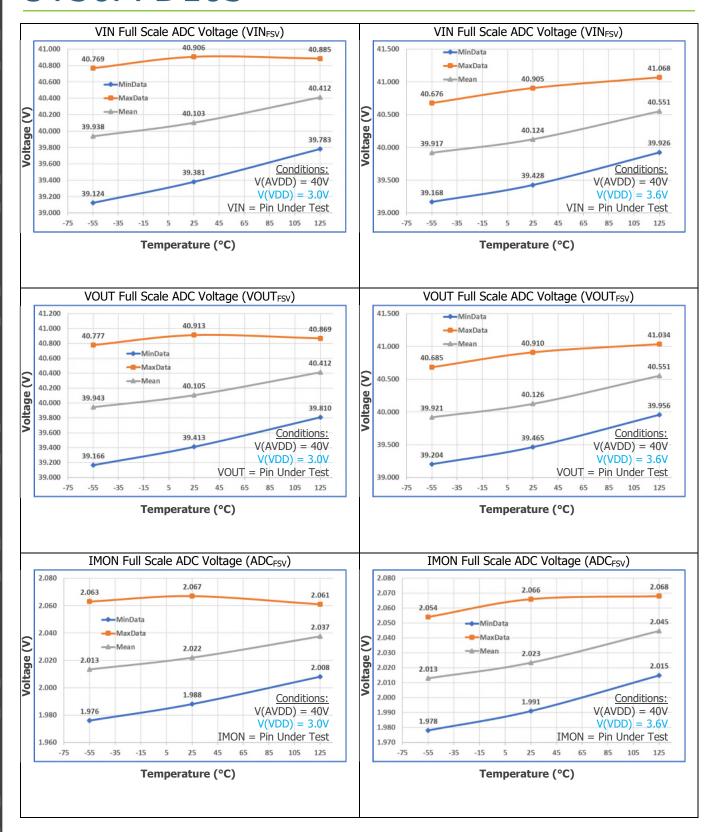

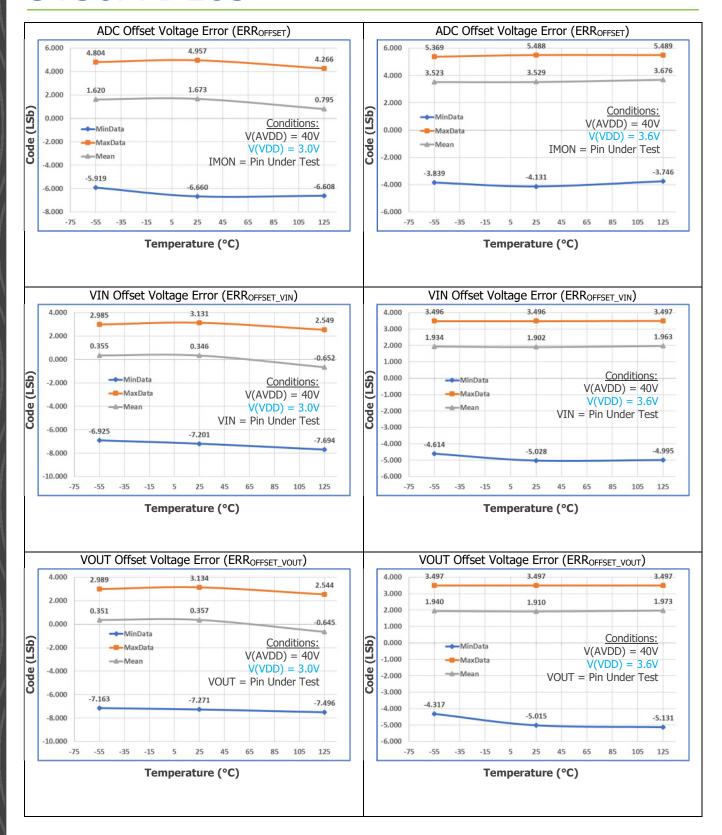

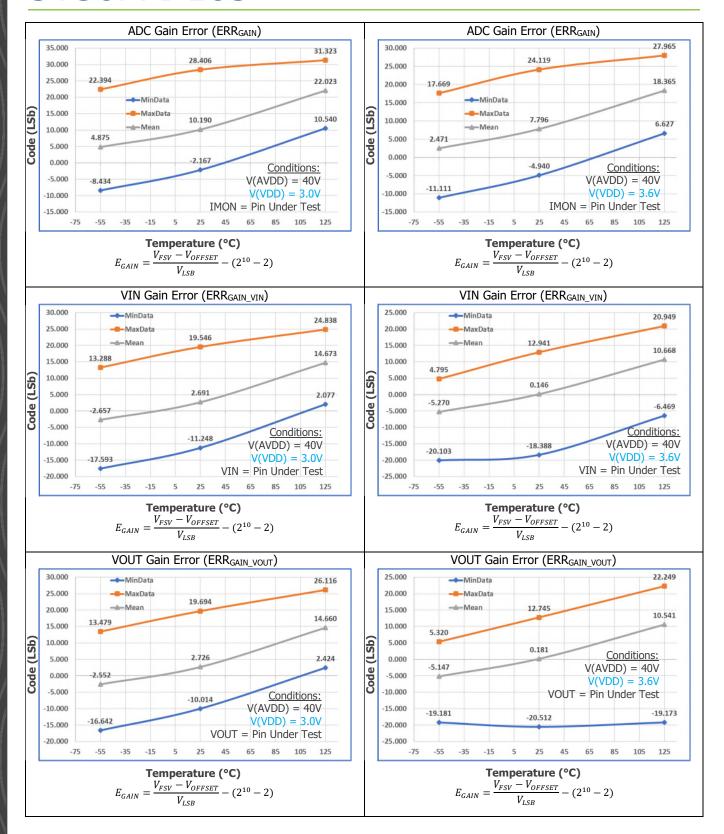

or by using the PMBus functionality to read the 10-bit digitized representation of the IMON voltage. The full-scale ADC voltage relating IMON is 2V with 1.6V corresponding to the user defined Overcurrent threshold.

### 6.4 Overcurrent Fault Protection

Internally, the Smart Power Switch Controller compares the IMON voltage to a reference voltage. When the voltage surpasses 1.6V, nominal, the C\_FAULT pin begins to charge. The SPSC includes a "hiccup" feature that charges and discharges C\_FAULT based on the over/under threshold voltage of IMON. The charge/discharge ratio is 20:1.

If the C\_FAULT pin rises to the 1.6V threshold, the device declares an overcurrent fault condition. The SPSC responds by treating the LOAD PFET as an eFuse, switching it off to remove the voltage source from the load. Simultaneously, the CURR LIM B output is driven low.

Once a current fault is detected, the GATE\_INR controlling the LOAD PFET's gate is latched OFF and a restart command must be received to restore power to the load. A restart command occurs when one of the device control pins (EN\_B, EN\_INR, MRST\_B, SLEEP\_B) is toggled HIGH-LOW-HIGH or PMBus Operation.7 is set to 1.

Alternatively, the PMBus interface may be used to program the number of allowable restart attempts and the cooldown period before the restart is initiated.

### 6.5 Short Circuit Break Fault Protection

While the Overcurrent Fault Protection allows the system to trigger a fault based on an arbitrarily long elevated current condition, the Short Circuit Fault Protection circuitry monitors for a significantly higher current condition and rapidly opens (eFuses) the circuit by disabling the LOAD PFET when the user defined threshold is crossed.

With a resistor (R<sub>FAST</sub>) installed between the SENSEP pin and the bus power side of the current sense resistor (R<sub>SENSE</sub>), the SPSC's Short-Circuit Fault comparator evaluates the voltage drop across the sense resistor and R<sub>FAST</sub>. As the load current increases, the voltage drop across R<sub>SENSE</sub> increases. When the voltage drop across R<sub>SENSE</sub> becomes large enough, the Short Circuit Fault comparator declares a fault condition; disabling the LOAD PFET within 500ns, typical.

## **UT36PFD103**

### 6.6 Voltage Fault Protection

By implementing a voltage divider between the input line voltage and the OVLO, UVLO pins and between the VOUT and FEEDBACK pins, the user can set thresholds for over-voltage (OVLO) and under-voltage (UVLO) faults on the input line voltage and for under-voltage (FEEDBACK) on the load side.

In the event of a fault on either UVLO or OVLO the G\_INR pin is driven to AVDD to disable the load PFET, PGOOD is driven low, and fault status information is updated in the PMBus fault response registers if PMBus functionality is enabled. A fault on FEEDBACK only affects the PGOOD output and corresponding PMBus status information.

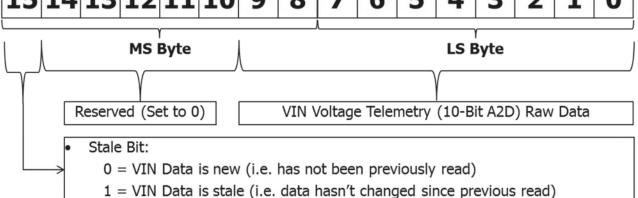

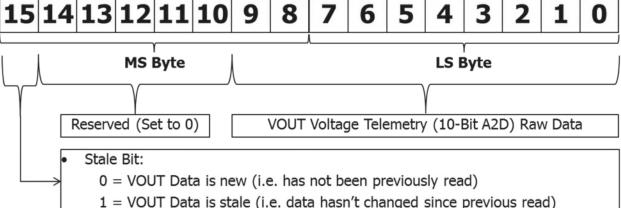

### 6.7 Voltage Monitoring

When using the SPSC's PMBus functionality, the voltage on pins VIN and VOUT are digitized to 10-bit with 40.00V being the full-scale voltage range. PMbus commands READ\_VIN and READ\_VOUT are used by power management host to obtain this telemetry along with the monitored current.

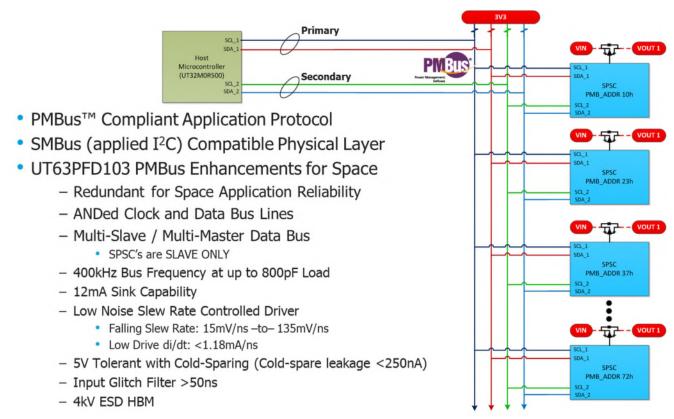

#### 6.8 PMBus

To get the maximum functionality from the SPSC, the PMBus feature must be utilized. Through the PMBus interface, a remote host controller can

- enable/disable the device

- configure Latched, Retrigger, and Pulsed modes

- obtain status on all fault conditions

- set retrigger and pulse delays

- defined retrigger count limits

- read 10-bit digitized representation of VIN, VLOAD, and IDS (aka IMON)

For spaceborne applications, system fault tolerance is often managed through redundancy. For this purpose, the SPSC provides a redundant SMBus port to access the common PMBus functions. The redundant SMBus implementation is coherent; allowing simultaneous PMBus access from the primary and secondary SMBus ports.

For applications that do not wish to use PMBus, the SPSC provides a PMB\_EN control signal to disable the PMBus functionality. The SPSC can perform bus switching, monitoring, and protection tasks without any PMBus involvement.

### 7 Absolute Maximum Ratings (1, 2)

Table 7-1: Absolute Maximum Ratings

| Symbol                            | Parameter                                              | Min             | Max        | Units |

|-----------------------------------|--------------------------------------------------------|-----------------|------------|-------|

| V <sub>HV_TECH</sub> (3, 4)       | High Voltage Technology Capability                     |                 | +56        | V     |

| AVDD (5)                          | Positive High Voltage Supply – Continuous<br>Operation | -0.5            | +40        | V     |

| HVIO1 (5)                         | High Voltage IO Group 1:<br>VIN & VOUT                 | -0.5            | +40        | V     |

| HVIO2                             | High Voltage IO Group 2: GATE_INR, GATE_OR, C_MILLER   | VZ13P5_HS - 0.5 | AVDD + 0.5 | ٧     |

| HVIO3                             | High Voltage IO Group 3:<br>RVRSP, SET, SENSEP, SENSEM | VZ5_HS - 0.5    | AVDD + 0.5 | ٧     |

| VDD                               | Positive Low Voltage Supply                            | -0.5            | +7.2       | V     |

| LVIO                              | Low Voltage Digital and Analog I/O within 3.3V Domain  | -0.5            | VDD + 0.5  | V     |

| $IO_{DC}$                         | Average Steady State IO Current                        | -10             | +10        | mA    |

| P <sub>D</sub> <sup>(6)</sup>     | Power Dissipation Permitted @ T <sub>C</sub> =125°C    |                 | 3.33       | W     |

| T <sub>J</sub>                    | Junction Temperature                                   |                 | +175       | °C    |

| θзс                               | Thermal Resistance, Junction-to-Case                   |                 | 15         | °C/W  |

| $T_{STG}$                         | Storage Temperature                                    | -65             | +150       | °C    |

| ESD <sub>HBM</sub> <sup>(7)</sup> | ESD Protection all Pins                                |                 | 2000       | V     |

| ESD <sub>HBM_SMBUS</sub> (7)      | Extended ESD Protection SMBus IO only                  |                 | 4000       | ٧     |

#### Note:

- Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond limits indicated in the operational sections of this specification are not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability and performance.

- 2) All absolute voltages referenced to AGND.

- 3) Technology voltage capability is provided to facilitate system derating requirements. This is not a recommended operating threshold.

- 4) Device compatible with CS106 EM Conducted Susceptibility testing.

- 5) This absolute maximum rating is limited by ground referenced ESD clamp, not by technology capability rating.

- 6) Per MIL-STD-883, method 1012, section 3.4.1, PD=(TJ(max)-TC(max))/θJC).

- 7) Per MIL-STD-883, method 3015.

## 8 Operational Environment

Table 8-1: Operational Environment

| Symbol      | Parameter                                                 | Limit             | Units                   |

|-------------|-----------------------------------------------------------|-------------------|-------------------------|

| TID (1)     | Total Ionizing Dose                                       | <mark>100</mark>  | krad(Si)                |

| SEL (2)     | Single Event Latchup Immunity                             | ≤ 100             | MeV-cm <sup>2</sup> /mg |

| SEGR (3, 4) | SEGR <sup>(3, 4)</sup> Single Event Gate Rupture Immunity |                   | MeV-cm <sup>2</sup> /mg |

| SEB (3)     | Single Event Burnout Immunity                             | <b>≤ 100</b>      | MeV-cm <sup>2</sup> /mg |

| SEU (5)     | SEU (5) Single Event Upset Immune                         |                   | MeV-cm <sup>2</sup> /mg |

| SET (5)     | Single Event Transient Immune                             | <mark>≤ 80</mark> | MeV-cm <sup>2</sup> /mg |

- 1) For devices procured with a total ionizing dose tolerance guarantee, post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A at an effective dose rate of 1 rad(Si)/sec up to maximum TID level procured.

- Performed at VDD = 3.6V & AVDD = 36V at 125°C.

- 3) Performed at VDD = 3.6V & AVDD = 36V at 25°C.

- 4) Performed with highest energy ion selected at normal incidence.

- Performed at VDD = 3.0V & AVDD = 36V at 25°C.

RELEASED September 2022

### 9 Recommended Operating Conditions (1)

Table 9-1: Recommended Operating Conditions

| Symbol             | Parameter                                                                                      | Min            | Max      | Units |

|--------------------|------------------------------------------------------------------------------------------------|----------------|----------|-------|

| T <sub>C</sub>     | Case Operating Temperature Range                                                               | -55            | +125     | °C    |

| AVDD (2)           | High Voltage Power Supply                                                                      | +8V            | +36V     | V     |

| VDD                | Low Voltage Digital and Analog Power Supply                                                    | +3.0           | +3.6     | V     |

| HVIO1              | VIN & VOUT Voltage Range                                                                       | 0              | AVDD+1   | V     |

| HVIO2              | GATE_OR, GATE_INR, & C_MILLER Voltage Range                                                    | VZ13P5_HSx (3) | AVDD+0.5 | V     |

| HVIO3              | RVRSP, SET, SENSEM & SENSEP Voltage Range                                                      | AVDD-0.5       | AVDD+0.5 | V     |

| LVIO               | Low Voltage Digital and Analog I/O within 3.3V Domain                                          | 0              | VDD      | V     |

| tRF <sub>DIG</sub> | Digital Input Rise & Fall Time (20%-80% of VDD) Pins: MRST_B, SLEEP_B, PMB_EN, VGS_DRV, PARITY |                | 50       | ns    |

| AGND (4)           | Analog Ground Return                                                                           | 0              |          | V     |

| DGND (4)           | Digital Ground Return                                                                          | AGND-10        | AGND+10  | mV    |

#### Note:

- 1) AVDD and VDD are referenced to AGND.

- 2) 36V maximum continuous operation already accounts for 65% de-rating from the 56V technology capability.

- 3) Refer to Table 10-1 for potential VZ13P5\_HSx voltages.

- 4) AGND and DGND shall be shorted together at a common point on the user's PCB.

### 10 Electrical Characteristics (1)

(AVDD = 8V to 36V, VDD =  $3.3V \pm 0.3V$ ,  $-55^{\circ}C < T_{C} < +125^{\circ}C$ ); Unless otherwise noted,  $T_{C}$  is per the temperature range ordered.

Table 10-1: Power Supply and Reference Characteristics

Unless otherwise noted, the following parameters are tested with VDD = 3.0V

| Symbol                        | Parameter                                                     | Conditions                                                   | Min          | Max         | Units |

|-------------------------------|---------------------------------------------------------------|--------------------------------------------------------------|--------------|-------------|-------|

| AVDD                          | High Voltage Power Supply                                     | AVDD = 8V to 36V;<br>Referenced to AGND                      | +8V          | +36         | V     |

| CBYP <sub>AVDD</sub>          | AVDD Bypass Capacitor                                         | Connect between AVDD & AGND,<br>1 each per AVDD pin          | 0.1          |             | μF    |

| VZ5_HS                        | High Voltage Logic Reference                                  | AVDD ≥ 8V                                                    | AVDD<br>-5.5 | AVDD<br>-4  | V     |

| CBYP <sub>VZ5_HS</sub>        | VZ5_HS Bypass Capacitor                                       | Connect between AVDD & VZ5_HS, 1 each per AVDD pin           | 0.1          |             | μF    |

| VZ13P5_HS1                    | High Voltage Gate Driver Reference                            | AVDD ≥ 15.5V; VGS_DRV = High                                 | AVDD<br>-15  | AVDD<br>-12 | V     |

| VZ13P5_HS2                    | High Voltage Gate Driver Reference                            | AVDD ≥ 10.5V; VGS_DRV = Low                                  | AVDD<br>-10  | AVDD<br>-7  | V     |

| VZ13P5_HS3 <sup>(2)</sup>     | High Voltage Gate Driver Reference                            | AVDD = 8V to 10.5V;<br>VGS_DRV=H or L                        | AGI          | ND          | V     |

| CBYP <sub>VZ13P5_HS</sub> (3) | VZ13P5_HS Bypass Capacitor                                    | Connect between AVDD & VZ13P5_HS, 1 each per AVDD pin        | 1            |             | μF    |

| VZ5_LS                        | Low Voltage Internal Regulator for Analog References & Biases | AVDD ≥ 8V<br>Referenced to AGND                              | +4.0         | +5.5        | V     |

| CBYP <sub>VZ5_LS</sub>        | VZ5_LS Bypass Capacitor                                       | Connect between VZ5_LS & AGND                                | 0.1          | -           | μF    |

| VDD                           | Low Voltage Power Supply                                      | Referenced to AGND                                           | +3           | +3.6        | V     |

| CBYP <sub>VDD</sub>           | VDD Bypass Capacitor                                          | Connect one each bypass cap from VDD to AGND and VDD to DGND | 0.1          |             | μF    |

- 1) All voltages referenced to DGND or AGND as appropriate.

- 2) For operation where 8V ≤ AVDD ≤ 10.5V, user should short VZ13P5\_HS to AGND to achieve maximum G\_INR & G\_OR potential.

- 3) CBYP<sub>VZ13P5\_HS</sub> must be at least 4 times larger than capacitance added to the C\_MILLER pin.

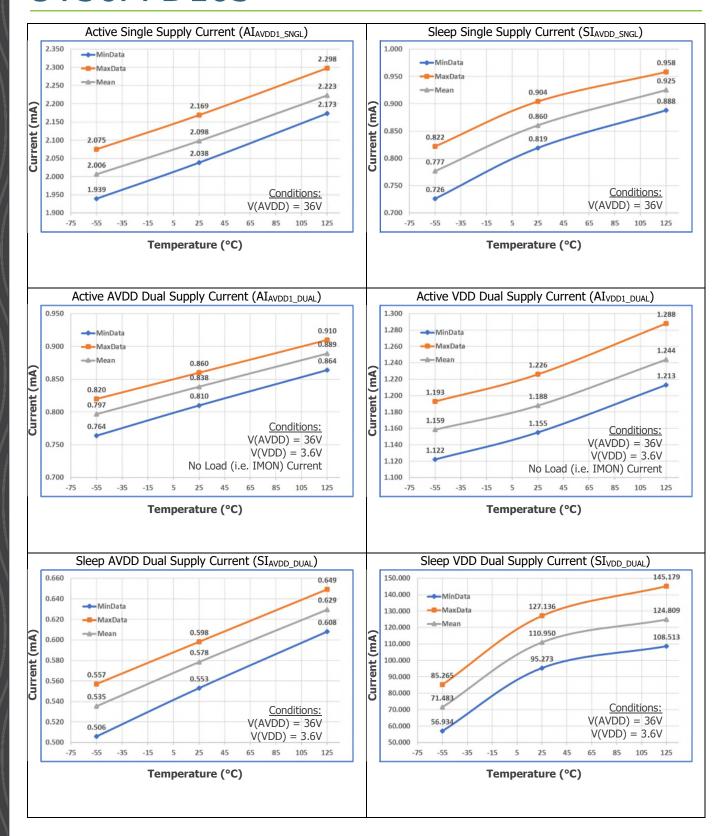

Table 10-2: Power Supply Current Consumption Characteristics

| Table 10 2: Fower Supply Current Consumption Characteristics |                                                 |                                                           |     |     |       |  |  |  |

|--------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------|-----|-----|-------|--|--|--|

| Symbol                                                       | Parameter                                       | Conditions                                                | Min | Max | Units |  |  |  |

| Single Supply                                                | Current Consumption                             |                                                           |     |     |       |  |  |  |

| Test conditions unless otherwise noted:                      |                                                 |                                                           |     |     |       |  |  |  |

| <ul><li>AVDD = +36V;</li></ul>                               |                                                 |                                                           |     |     |       |  |  |  |

|                                                              | DD_DIS, EN_B = Low                              |                                                           |     |     |       |  |  |  |

|                                                              | R, EN_OR, MRST_B, SLEEP_B, PMB_EN = $Hightimes$ | jh                                                        |     |     |       |  |  |  |

| ,                                                            | ENSEM, VOUT ≈ AVDD                              |                                                           |     |     |       |  |  |  |

| No VO                                                        | UT current load; No Fault; C_TIMER = Open;      | 400kHz activity on PMBus IO                               |     |     |       |  |  |  |

| AI <sub>AVDD1_SNGL</sub>                                     | Active High Voltage Supply Current              |                                                           |     | 2.8 | mA    |  |  |  |

|                                                              |                                                 | EN_B=MRST_B=SLEEP_B=High;                                 |     |     |       |  |  |  |

| $QI_{AVDD\_SNGL}$                                            | Quiescent High Voltage Supply Current           | EN_INR=EN_OR=PMB_EN=Low;                                  |     | 2.7 | mA    |  |  |  |

|                                                              |                                                 | VOUT=Float; No PMBus Activity                             |     |     |       |  |  |  |

| $SI_{AVDD\_SNGL}$                                            | Sleep High Voltage Supply Current               | SLEEP_B=Low; VOUT=Float                                   |     | 1.4 | mA    |  |  |  |

| <b>Dual Supply C</b>                                         | urrent Consumption                              |                                                           |     |     |       |  |  |  |

|                                                              | unless otherwise noted:                         |                                                           |     |     |       |  |  |  |

| <ul> <li>AVDD</li> </ul>                                     | = +36V; VDD = +3.6V                             |                                                           |     |     |       |  |  |  |

|                                                              | DD_DIS=High                                     |                                                           |     |     |       |  |  |  |

| • EN_B :                                                     |                                                 |                                                           |     |     |       |  |  |  |

|                                                              | R, EN_OR, MRST_B, SLEEP_B, PMBEN = High         | 1                                                         |     |     |       |  |  |  |

|                                                              | ENSEM, VOUT ≈ AVDD                              |                                                           |     |     |       |  |  |  |

| No VO                                                        | UT current load; No Fault; C_TIMER = Open;      | 400kHz activity on PMBus IO                               |     | 1 1 |       |  |  |  |

| AI <sub>AVDD1_DUAL</sub>                                     | Active High Voltage Supply Current              |                                                           |     | 1.7 | mA    |  |  |  |

| AI <sub>VDD1_DUAL</sub>                                      | Active Low Voltage Supply Current               |                                                           |     | 1.7 | mA    |  |  |  |

| QI <sub>AVDD_DUAL</sub>                                      | Quiescent High Voltage Supply Current           | EN_B=MRST_B=SLEEP_B=High;                                 |     | 1.6 | mA    |  |  |  |

| $QI_{VDD\_DUAL}$                                             | Quiescent Low Voltage Supply Current            | EN_INR=EN_OR=PMB_EN=Low;<br>VOUT=Float; No PMBus Activity |     | 1.6 | mA    |  |  |  |

| SI <sub>AVDD_DUAL</sub>                                      | Sleep High Voltage Supply Current               | <br>  SLEEP B=Low; VOUT=Float                             |     | 1   | mA    |  |  |  |

| STVDD DUM                                                    | Sleen Low Voltage Supply Current                | SLLLF_D-LOW, VOOT-Float                                   |     | 250 | нΑ    |  |  |  |

Note:

$SI_{\text{VDD\_DUAL}}$

Sleep Low Voltage Supply Current

250

μΑ

<sup>1)</sup> All voltages referenced to DGND or AGND as appropriate.

Table 10-3: Low Voltage Digital I/O Electrical Characteristics

Unless otherwise noted, the following parameters are tested with AVDD=8V and VDD = 3.0V & 3.6V.

| Symbol                             | Parameter                                                      | Conditions                                            | Min            | Max             | Units |

|------------------------------------|----------------------------------------------------------------|-------------------------------------------------------|----------------|-----------------|-------|

|                                    | ital Inputs (Referenced to DGND) DRV, MRST_B, PMB_EN           |                                                       |                |                 |       |

| V <sub>IH</sub>                    | High Level Input Voltage                                       | For VGS_DRV only AVDD = 36V                           | 0.7*           |                 | V     |

| VIH                                | night Level Input Voltage                                      | For VGS_DRV only AVDD = 36V                           | VDD            | 2.01            | V     |

| $V_{\text{IL}}$                    | Low Level Input Voltage                                        | For VGS_DRV only AVDD = 36V                           |                | 0.3*<br>VDD     | V     |

| ${ m I}_{ m IL}$                   | Input Leakage Current                                          | VDD=3.6V<br>INPUT = 0V or VDD                         | -1             | 1               | μA    |

| C <sub>IN</sub> (1)                | Input Capacitance                                              |                                                       |                | <mark>15</mark> | pF    |

| Standard Digi<br>SLEEP_B           | ital Inputs with Pull-Ups and (Referen                         | ced to DGND)                                          |                |                 |       |

| V <sub>IH</sub>                    | High Level Input Voltage                                       |                                                       | 0.7*<br>VDD    |                 | V     |

| V <sub>IL</sub>                    | Low Level Input Voltage                                        |                                                       | 1==            | 0.3*<br>VDD     | V     |

| $I_{IL\_PU}$                       | Input Leakage Current Pull-Up                                  | VDD=3.6V; INPUT=0V                                    | -20            | -5              | μA    |

| $I_{\mathrm{IL}}$                  | Input Leakage Current                                          | VDD=3.6V; INPUT= VDD                                  |                | 2               | μA    |

| C <sub>IN</sub> (1)                | Input Capacitance                                              |                                                       |                | <mark>15</mark> | pF    |

| <b>V Digital Inp</b><br>NT_VDD_DIS | outs (Referenced to DGND)                                      |                                                       |                |                 |       |

| V <sub>IH</sub>                    | High Level Input Voltage                                       |                                                       | 0.7*<br>VZ5_LS |                 | ٧     |

| $V_{\text{IL}}$                    | Low Level Input Voltage                                        |                                                       | 125_25         | 0.3*<br>VZ5_LS  | ٧     |

| $\mathbf{I}_{IL}$                  | Input Leakage Current                                          | VZ5_LS=5V; VDD=3.6V;<br>INPUT = 0V or VZ5_LS          | -1             | 1               | μA    |

| C <sub>IN</sub> (1)                | Input Capacitance                                              |                                                       |                | <mark>15</mark> | pF    |

| ernary Input<br>ADDR0-ADDR4        | ts (Referenced to DGND)                                        |                                                       |                |                 |       |

| V <sub>IH_TERN</sub>               | High Level Input Voltage                                       |                                                       | VDD<br>-0.3    |                 | ٧     |

| V <sub>IM_TERN</sub> (4)           | Mid Level Input Voltage                                        |                                                       | VDD/2<br>-0.3  | VDD/2<br>+0.3   | ٧     |

| V <sub>IL_TERN</sub>               | Low Level Input Voltage                                        |                                                       | 0.0            | 0.6             | V     |

| I <sub>ILL</sub> (3)               | Low Level Input Leakage Current<br>While Latching ADDR4-ADDR0  | MRST_B=Low; VDD=3.6V; Pin under test: VADDR[x]=0V;    | -100           | -20             | μA    |

| I <sub>ILM</sub> (3,4)             | Mid Level Input Leakage Current<br>While Latching ADDR4-ADDR0  | MRST_B=Low; VDD=3.6V; Pin under test: VADDR[x]=VDD÷2; | 3              | 40              | μΑ    |

| I <sub>ILH</sub> (3)               | High Level Input Leakage Current<br>While Latching ADDR4-ADDR0 | MRST_B=Low; VDD=3.6V; Pin under test: VADDR[x]=3.6V;  | 20             | 100             | μΑ    |

| C <sub>IN</sub> (1)                | Input Capacitance                                              |                                                       |                | <mark>15</mark> | pF    |

| <b>pen Drain D</b><br>GOOD, CURR   | igital Outputs (Referenced to DGND)                            |                                                       |                |                 |       |

| V <sub>OL</sub>                    | Low Level Output Voltage                                       | ISINK = 4mA                                           |                | 0.4             | ٧     |

| $I_{SC}^{(2)}$                     | Output Short Circuit Current                                   | VDD=3.6V; OUTPUT= VDD                                 | 25             | 50              | mA    |

| $\mathbf{I}_{OZ}$                  | Output Leakage Current                                         | VDD=3.6V;<br>OUTPUT = 0 or VDD;                       | -2             | 2               | μΑ    |

| Cout (1)                           | Input Capacitance                                              |                                                       |                | <mark>15</mark> | pF    |

# **UT36PFD103**

| Symbol                          | Parameter                                                                                                 | Conditions                      | Min | Max             | Units |  |  |  |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------|-----|-----------------|-------|--|--|--|--|--|

|                                 | SMBus I/O with Schmitt Trigger Inputs (Referenced to DGND) SMBCLK1, SMBDIO1, SMBCLK2, SMBDIO2, SMBALERT_B |                                 |     |                 |       |  |  |  |  |  |

| $V_{T+}$                        | Positive Going Input Threshold Voltage                                                                    |                                 |     | 1.89            | V     |  |  |  |  |  |

| V <sub>T</sub> -                | Negative Going Input Threshold Voltage                                                                    |                                 | 0.8 |                 | ٧     |  |  |  |  |  |

| V <sub>H</sub>                  | Threshold Voltage Hysteresis                                                                              |                                 | 80  | 550             | mV    |  |  |  |  |  |

| V <sub>OL</sub>                 | Low Level Output Voltage                                                                                  | ISINK = 12mA                    |     | 0.4             | V     |  |  |  |  |  |

| I <sub>SC1</sub> <sup>(2)</sup> | Output Short Circuit Current                                                                              | VDD=3.6V; OUTPUT=VDD            | 65  | 125             | mA    |  |  |  |  |  |

| I <sub>OZ</sub>                 | Output Leakage Current                                                                                    | VDD=3.6V;<br>OUTPUT = 0 or VDD; | -2  | 2               | μA    |  |  |  |  |  |

| C <sub>IO</sub> (1)             | Input Capacitance                                                                                         |                                 |     | <mark>15</mark> | pF    |  |  |  |  |  |

| C <sub>SMB_LOAD</sub> (2)       | Total SMBus Load Capacitance                                                                              |                                 |     | 800             | pF    |  |  |  |  |  |

- 1) 2) 3) Guaranteed by characterization; not tested.

- Provided as applications information only, neither guaranteed nor tested.

- Guaranteed by design, not tested.

- For ADDR4, only, the mid point ternary specifications do not apply because only a HIGH and LOW state are required for the address decoding logic.

# UT36PFD103

### Table 10-4: Low Voltage Analog I/O Electrical Characteristics

|                                   | e noted, the following parameters are teste                            |                                                                         |                 |                 |       |

|-----------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------|-----------------|-------|

| Symbol                            | Parameter                                                              | Conditions                                                              | Min             | Max             | Units |

| <b>Current Monito</b> i<br>IMON   | r and Overcurrent Analog Comparator (refe                              | renced to AGND)                                                         |                 |                 |       |

| V <sub>IMON_RANGE</sub> (4)       | IMON Operating Voltage Range                                           |                                                                         | 0               | VDD             | ٧     |

| V <sub>IMON_CL</sub>              | IMON Voltage Threshold at Current Limit                                | Detect by ΔV on C_FAULT Pin                                             | 1.              | 6               | V     |

| V <sub>IMON_TOL</sub> (1)         | IMON Voltage Threshold Tolerance                                       |                                                                         | -60             | 60              | mV    |

| I <sub>IMON_CL</sub> (4)          | IMON Current at Current Limit                                          | V <sub>IMON</sub> = 1.6V                                                | -               | 1               | mA    |

|                                   |                                                                        | $V_{T\_CL} = 25mV$                                                      | ± :             | 1.5             |       |

| $I_{IMON\ TOL}^{\ (2,\ 4)}$       | IMON Current Tolerance at Current Limit                                | V <sub>T_CL</sub> = 50mV                                                | ±               | 2               | %     |

|                                   |                                                                        | V <sub>T_CL</sub> = 100mV                                               | ± 2             | 2.5             |       |

| Ioz                               | Output Leakage Current                                                 | VDD=3.6V; V <sub>AVDD</sub> =V <sub>SENSEM</sub><br>OUTPUT = 0V or VDD  | -2              | 2               | μA    |

| R <sub>IMON</sub> (5)             | IMON Shunt Resistor                                                    | Recommended 1% Tolerance                                                | 1.              | 6               | kΩ    |

| C <sub>IMON</sub> <sup>(5)</sup>  | IMON Low Pass Filter Capacitance                                       | $45kHz LPF \approx \frac{1}{2\pi * R_{IMON} * C_{IMON}}$                | 2.2             |                 | nF    |

| C <sub>IN</sub> (3)               | Pin Capacitance                                                        |                                                                         |                 | <mark>25</mark> | pF    |

|                                   | ator Inputs with Hysteresis and (referenced N_OR, UVLO, OVLO, FEEDBACK | to AGND)                                                                |                 | _               |       |

| $V_{T+}$                          | Positive Going Input Threshold Voltage                                 |                                                                         |                 | 1.73            | V     |

| $V_{T-}$                          | Negative Going Input Threshold Voltage                                 |                                                                         | 1.43            |                 | V     |

| $V_{H}$                           | Threshold Voltage Hysteresis                                           |                                                                         | 35              | 100             | mV    |

| $\mathbf{I}_{	ext{IL}}$           | Input Leakage Current                                                  | VDD=3.6V<br>0V ≤ INPUT ≤ VDD;                                           | -2              | 2               | μΑ    |

| C <sub>IN</sub> (3)               | Pin Capacitance                                                        |                                                                         |                 | <mark>15</mark> | pF    |

| <b>Adjustable Faul</b><br>C_FAULT | t Timer (referenced to AGND)                                           |                                                                         |                 |                 |       |

| $V_{T_{FAULT}}$                   | Nominal Input Voltage Threshold                                        | Detect by change on CURR_LIM_B                                          | 1.              | 6               | ٧     |

| $V_{T\_TOL}$                      | Input Threshold Tolerance                                              |                                                                         | -45             | 45              | mV    |

| I <sub>CHARGE</sub>               | Charging Current                                                       |                                                                         | -125            | -90             | μA    |

| IDISCHARGE                        | Discharging Current                                                    |                                                                         | 4.5             | 6.0             | μΑ    |

| C <sub>FAULT_INT</sub> (3)        | Internal Pin Capacitance                                               |                                                                         |                 | <mark>30</mark> | pF    |

| Adjustable Osci                   | llator (referenced to <mark>DGND</mark> )                              |                                                                         |                 | •               |       |

| V <sub>T+</sub>                   | Positive Going Input Threshold Voltage                                 |                                                                         |                 | 1.45            | V     |

| $V_{T-}$                          | Negative Going Input Threshold Voltage                                 |                                                                         | 0.6             |                 | V     |

| V <sub>H</sub>                    | Threshold Voltage Hysteresis                                           |                                                                         | 225             | 450             | m۷    |

| Icharge                           | Charging Current                                                       |                                                                         | <mark>-6</mark> | <del>-4.5</del> | μA    |

| IDISCHARGE                        | Discharging Current                                                    |                                                                         | 4.5             | 6               | μA    |

| F <sub>C_TIMER</sub> (8)          | C_TIMER Frequency                                                      | C_TIMER pin capacitance ~10nF                                           | 600             | 1000            | Hz    |

| DC <sub>C_TIMER</sub>             | C_TIMER Duty Cycle                                                     | C_TIMER pin capacitance ~10nF                                           | 45              | 55              | %     |

| C <sub>TIMER_INT</sub> (3)        | Internal Pin Capacitance                                               |                                                                         |                 | <mark>30</mark> | pF    |

| Analog Compara                    | ator Error Sources                                                     |                                                                         | L               |                 |       |

| EN_B, EN_INR, EN                  | N_OR, UVLO, OVLO, FEEDBACK, IMON, C_FAULT,                             |                                                                         | <u> </u>        | 1               |       |

| V <sub>os</sub> <sup>(4,6)</sup>  | Comparator Offset Voltage                                              | Threshold difference between comparator positive and negative terminals | -10             | +10             | mV    |

| (4.6)                             | 4 CV D. C. VV II. T. I                                                 |                                                                         | -40             | 1.40            | mV    |

| V1P6 <sub>REF_TOL</sub> (4,6)     | 1.6V Reference Voltage Tolerance                                       |                                                                         | -40             | +40             | IIIV  |

## **UT36PFD103**

| Symbol                                          | Parameter                                | Conditions                      | Min Max |       | Units |

|-------------------------------------------------|------------------------------------------|---------------------------------|---------|-------|-------|

| Bias Current Generator (reference to AGND) IREF |                                          |                                 |         |       |       |

| R <sub>IREF</sub> (5)                           | Required IREF Load Resistor              | Connected between IREF and AGND | 24.9    |       | kΩ    |

| R <sub>IREF_TOL</sub> (4)                       | Recommended IREF Load Resistor Tolerance |                                 | ±       | 1     | %     |

| V <sub>IREF</sub>                               | Voltage at IREF Pin                      |                                 | 0.925   | 1.075 | V     |

| C <sub>IREF</sub> (3,7)                         | IREF Pin External Load Capacitance       |                                 |         | 20    | pF    |

#### Note:

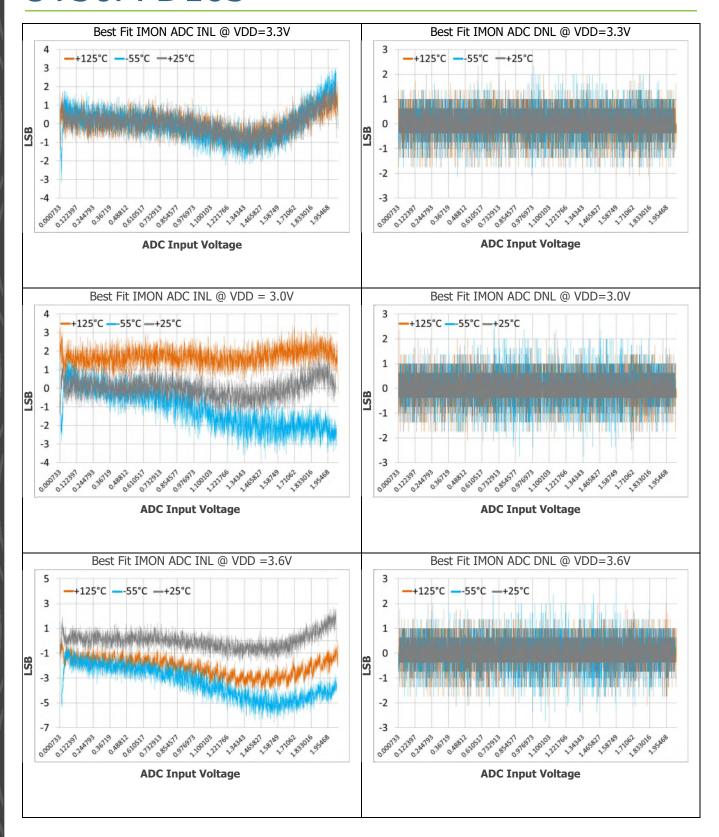

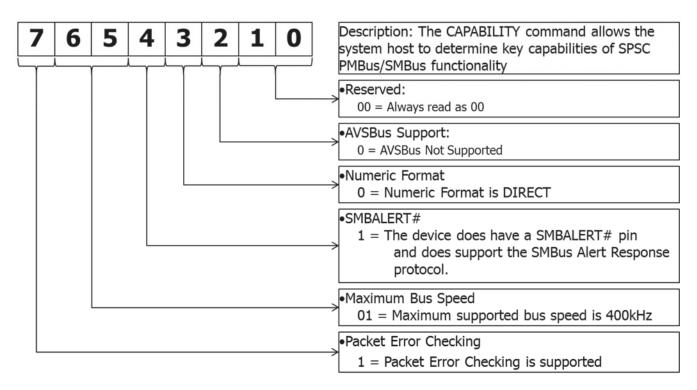

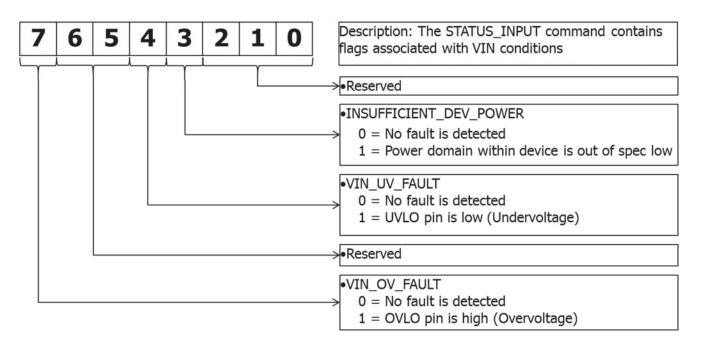

- 1) V<sub>IMON\_TOL</sub> only includes comparator error sources that are specific to the device: Offset Voltage, Reference Accuracy, and Noise. Effective current limit detection tolerance will increase in a Root Sum Square (RSS) fashion with I<sub>IMON\_TOL</sub> and user dependent error sources such as R<sub>IMON</sub>, R<sub>SENSE</sub> and R<sub>SET</sub> tolerances.